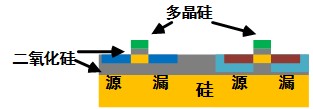

SiC 平面mosfet 器件的工作原理

SiC(碳化硅)平面 MOSFET(金属氧化物半导体场效应晶体管)是一种基于碳化硅材料的功率半导体器件,其工作原理与传统的硅基平面 MOSFET 类似,但得益于 SiC 材料的优异特性(如高击穿电场、高...

转发:5次“再就业”,张汝京:一切都可以从头再来

大不了从头再来。”没有人比张汝京更有底气说这句话。 在半导体产业沉浮了42年,5次“再就业”,张汝京的每一次“从头再来”,都是一段精彩的故事。 张汝京是南京人,生于南京。 1949年的特殊时代背景下,不到1岁的张汝京便因举家南迁去到了台湾,直到在台湾大学机器工程专业毕业。此后,他先后去到纽约州立大学和南卫理公会大学进修,分别获得了工程科学硕士与电子工程博士学位。

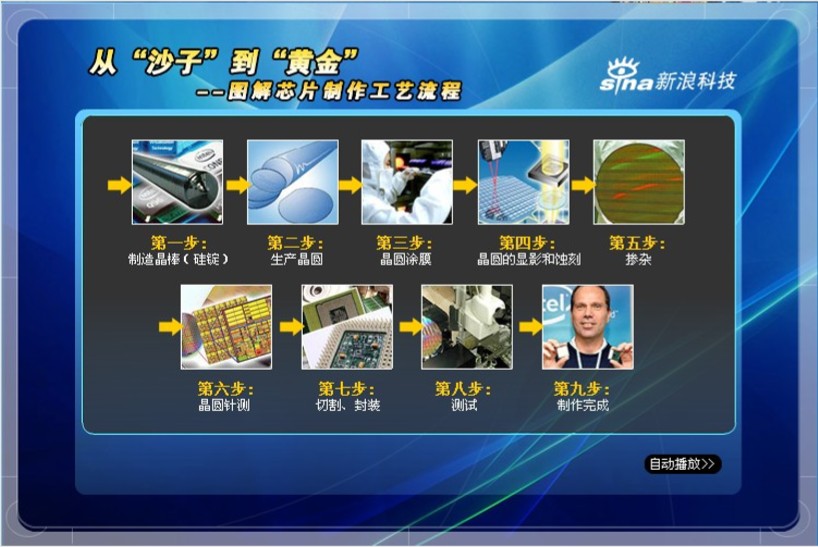

从“沙子”到“黄金” --- 图解芯片制作流程

从“沙子”到“黄金” --- 图解芯片制作流程

【芯片】我在中芯国际的往事&中芯国际深度解析

以下评论来自我们会员投的芯片公司创始人。这个产业需要技术/人/时间的积淀,很难跨越式发展。他们也是在摸索了数年,交了很多辆奔驰车的学费之后,才做出了细分领域唯一能量产交货的产线。

细数中芯国际四代CEO掌门人交替与未来变途

世事总在多变中有诡谲的一面。两岸半导体巨头台积电、中芯国际在“接班人”的背景与命运安排大不同:台积电第二代接班人至今“悬而未决”;然这一头,中芯国际的CEO,千帆过尽,已接连走马换了四任...

半导体技术发展的科普知识

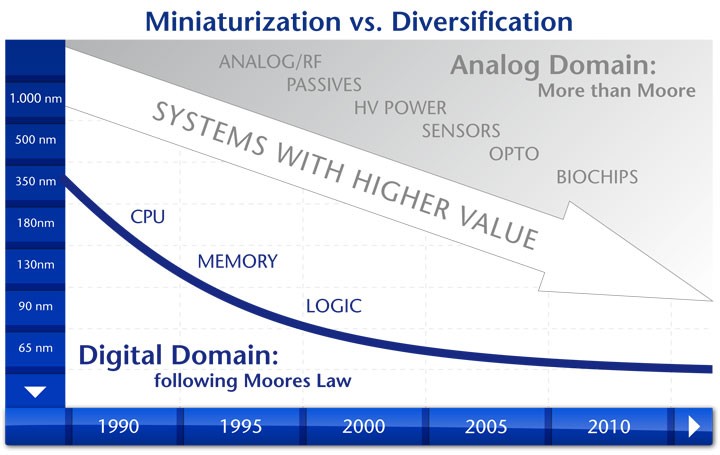

先简单讲摩尔定律(Moore's Law),就是从七八十年代的微米级工艺,到90年代的Sub-micron(<1um)、Deep Sub micron (<0.35),一路走到纳米技术。

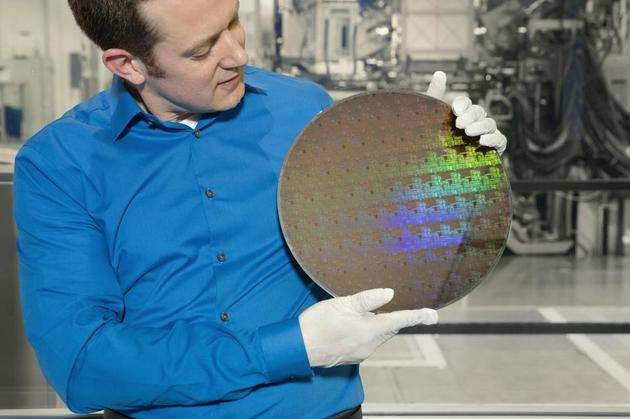

中国46座晶圆制造厂最新情况跟踪

2018年,芯思想研究院对国内晶圆生产线的情况进行了长期深入的跟踪调研。 根据芯思想研究院的统计,截止2018年底我国12英寸晶圆制造厂装机产能约60万片;8英寸晶圆制造厂装机产能约90万片;6...

2019年,中国晶圆代工产业最缺的是什么?

近两年中国大陆各地掀起的建厂潮引发了市场对产能过剩的忧虑,进入2019年,这种担忧将走向何方? 尽管中美贸易局势紧张和集成电路市场放缓,中国仍继续推进晶圆代工行业发展...

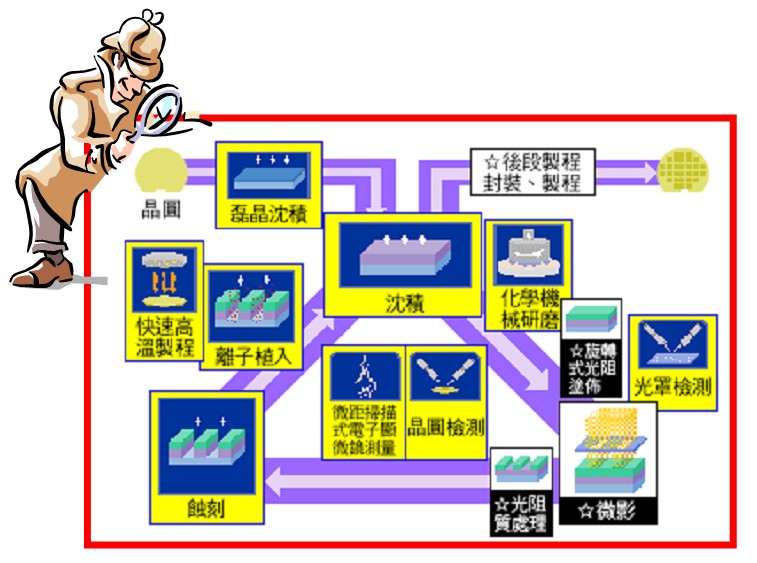

半导体集成电路PIE常识

1. 何谓PIE? PIE的主要工作是什幺? 答:Process Integration Engineer(工艺整合工程师), 主要工作是整合各部门的资源, 对工艺持续进行改善, 确保产品的良率(yi...

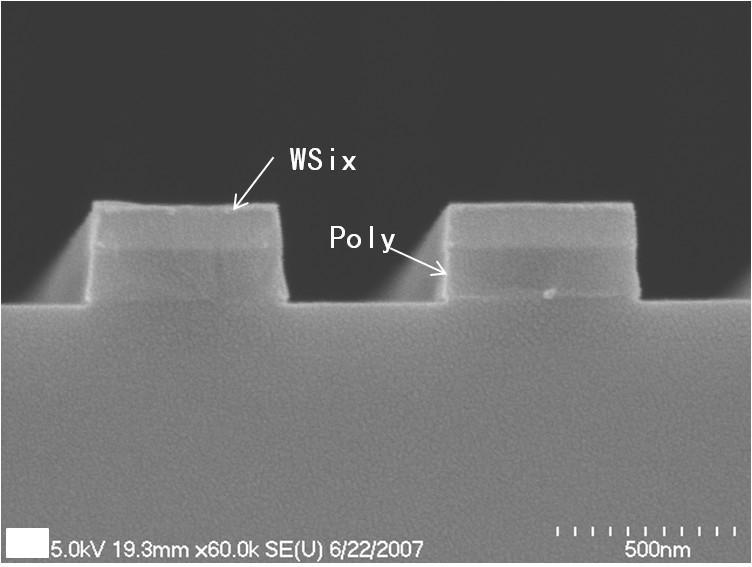

《Silicidation》-难熔金属硅化物--- 绝对经典,转载勿怪。

介绍一下,一直在看《芯苑》博客里面的技术文章,这篇是对Silicide最贴切的介绍。 文章来自:http://ic-garden.cn/?p=829 随着半导体线宽的等比例缩小,从微米级到深亚微米到纳米级,由于R*C...

晶圆做成芯片的工艺流程

1.湿洗 用各种化学试剂保持硅晶圆表面没有杂质 2.光刻 用紫外线透过【蒙版】照射硅晶圆 被照到的地方就会容易被清洗掉 没有被照射到的地方就会保持原样 于是就可以在硅晶圆上面刻出来...

SOI (Silicon-on-Insulator) 技术:

SOI (Silicon-on-Insulator) 技术: 传统CMOS技术的缺陷在于:衬底的厚度会影响片上的寄生电容,间接导致芯片的性能下降。 SOI技术主要是将源极/漏极和硅片衬底分开,以达到(部分)消除寄生电容...

Line 和 DUV 分别用什么样式的光阻?各个光阻特性如何?

To achieve sub-wavelength lithography results,resist rechnology - like the phase shifting masks,scanner optics and inspection techniques- is pushed to its absolute limit. Most impo...

半导体晶圆制造基础知识

ZERO OXIDE 的作用是什么? 第一是为后序的ZERO PHOTO时做PR的隔离,防止PR直接与Si接触,造成污染。

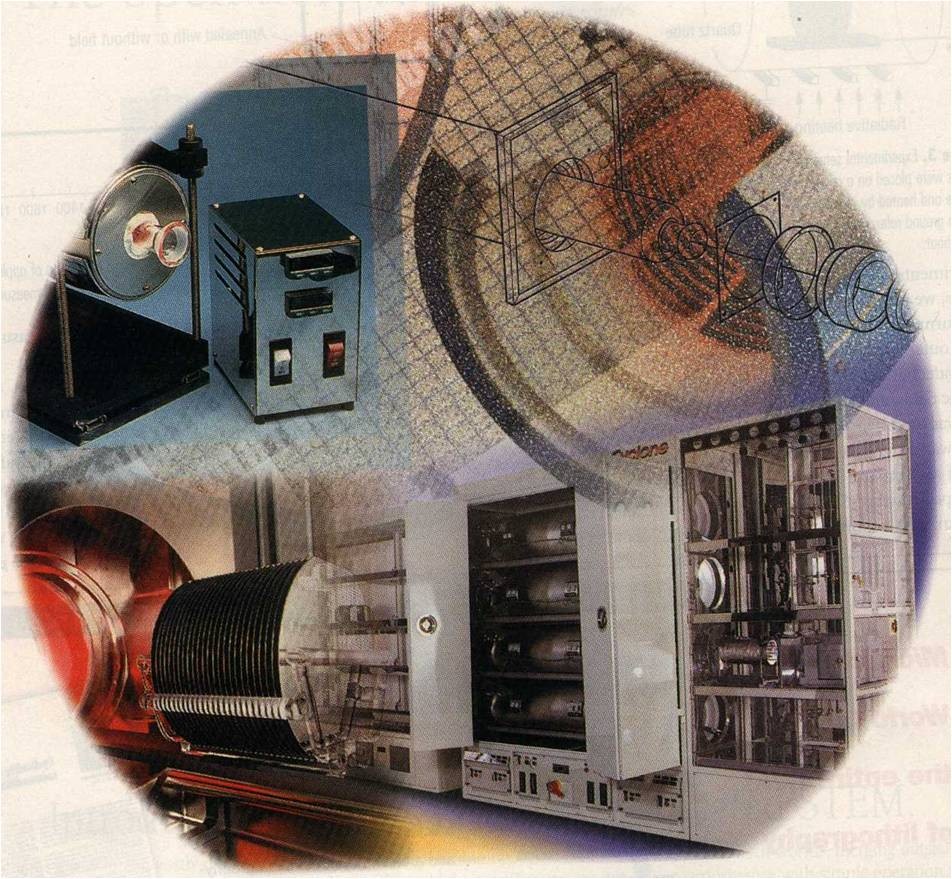

Unit Process–Diffusion(扩散)

今天的主题是扩散(diffusion),也有说炉管的,因为这个process都是要用到炉管的(那时候开玩笑说我是烧炉子的,就是干这个的。我刚毕业做过几个月这个,因为没有燃烧柜,直接H2+O2进管子,看着湿氧点火的火苗从管口喷出来很激动)。这里面分两块一个是氧化(oxidation)一个是推阱/激活,后者单纯就是给热过程(Thermal budget)让掺杂原子激活或者推到指定的深度。当然还有一个合金(Alloy)。

晶圆到芯片的工艺流程

晶圆到芯片的工艺流程1.湿洗用各种化学试剂保持硅晶圆表面没有杂质2.光刻用紫外线透过【蒙版】照射硅晶圆 被照到的地方就会容易被清洗掉 没有被照射到的地方就会保持原样 于是就可以在硅晶圆上...

SILICIDE、SALICIDE和POLYCIDE工艺的整理

SILICIDE、SALICIDE和POLYCIDE工艺的整理SILICIDE、SALICIDE和POLYCIDE (转载)工艺中经常会碰到。。呵呵。。权当抛砖引玉了,不准确的地方还希望大家指出讨论之~~首先,这三个名词对应的...

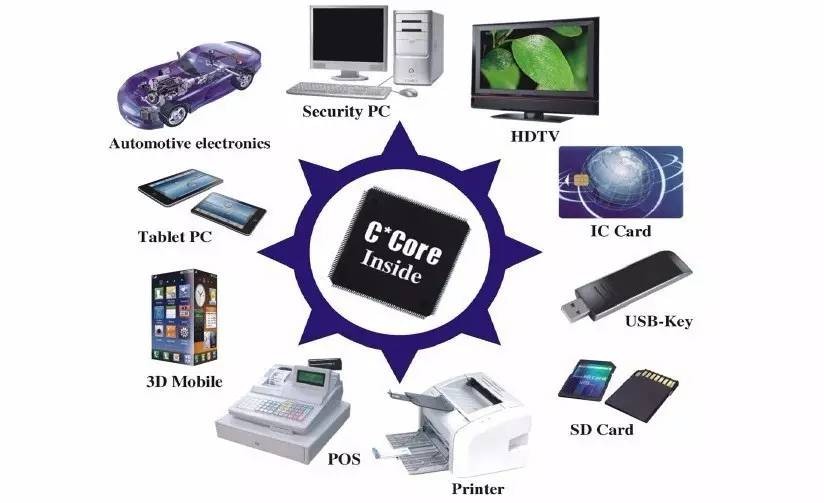

半导体或芯片的90nm、65nm 、0.25um、0.18um、工艺指的是什么?

半导体或芯片的90nm、65nm 、0.25um、0.18um等是IC工艺先进水平的主要指标。这些数字表示制作半导体或芯片的技术节点(technologynode),也称作工艺节点。IC生产工艺可达到的最小导线宽度,...

对Fab PIE 的最确切解读

很多人都想做PIE,包括应届生,有经验的module,我想原因很简单,在fab中,PIE学到东西最多,技术含量最高,最容易跳槽。我的意思并不是PIE一定比PE更牛,而是说在半导体整个技术层面上来说,PIE更加全面,因此也带来一个公认的结论,在对每个process的理解上,PIE不如PE理解得深刻。

今天,有什么经验需要分享呢?

立即撰写