在讲Spacer的Process理论之前,先讲下Spacer的作用,为什么要有这么个结构?这样你们才能永远记住它。

我们这些80后做半导体PIE的一出道就接触的是1.0um以下,我们称之为亚微米制程(到0.25um以下,我们称之为深亚微米, deep sub-micron)。而我们在亚微米以及深亚微米时代随着栅极长度/沟道长度的减小,主要面对的技术难题除了穿通(Punch Through)就是沟道电场(Channel Electric Field)导致的热载流子效应,前面的文章有详细讲解,这个我就不赘述了。主要是由于耗尽区宽度延展进入沟道,导致有效沟道长度变窄,所以等效加在沟道上的电场则增加(Vd/Leff),导致了沟道载流子碰撞能增加产生新电子空穴对(Electron-Hole pair),进而形成热载流子注入效应(HCE or HCI, Effect or Injection)。

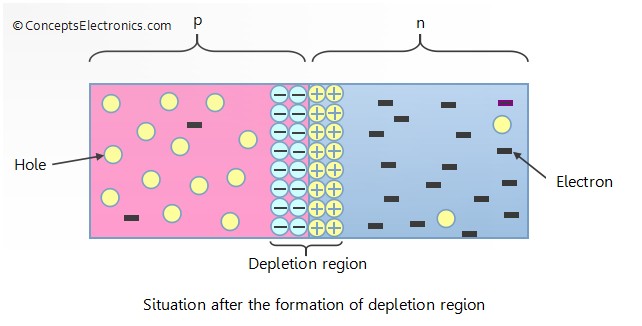

那我们如何防止沟道的热载流子效应?从上面的描述看,你只有减少耗尽区宽度来提高Leff,所以再次回到PN结的基本理论,如何减小耗尽区宽度?一方面,要么增加沟道区域的浓度也就是防穿通注入(NAPT Implant),或者Advance制程的Pocket implant都可以,因为沟道区域的浓度增加可以抑制耗尽区宽度延伸。另外一方面,就是降低Source/Drain这边的PN结浓度,这样也可以降低沟道区域的耗尽区宽度。(想不通的话再去前面的文章补习一下PN的理论啊~)。前者可以抑制穿通,但不可能一直提高浓度,毕竟会影响沟道开启电压,所以必须想法走第二条路。于是乎诞生了LDD(Low Doped Drain),做了一个低掺杂的漏极做为N+_S/D的Junction的过渡区,从原来的N+/PW的PN结过渡到了NLDD-/PW了,所以PW那边的耗尽区宽度自然就窄了。

Spacer的作用是什么?上面讲了一堆的热载流子效应,以及LDD抑制热载流子效应,可是这个和Spacer有什么关系呢?它又是怎么形成的呢?这才是本章讨论的重点。

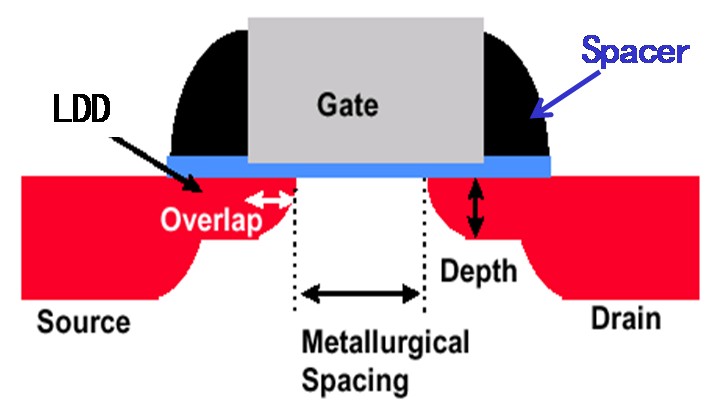

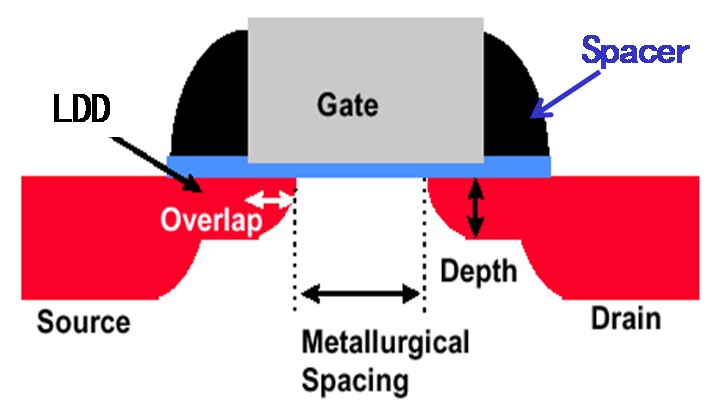

首先我们看器件结构,LDD都是在Spacer下面,这样就容易理解了,这个Spacer其实就是为了形成这个低浓度LDD的,我们的LDD是靠implant离子注入形成的,但是implant区域对这个器件来讲是真个器件注入的,所以硅露出来的地方都要被打到(Source/drain),所以等打完低浓度的LDD implant之后,再形成Spacer,再打Source/Drain高浓度 implant,则LDD区域被Spacer挡住了而留下来。(Flow sequence: PO1 ET->NLDD PH/IMP -> PLDD PH/Imp -> Spacer formation -> N+ Source/Drain PH/Implant ->P+ Source/Drain PH/implant)

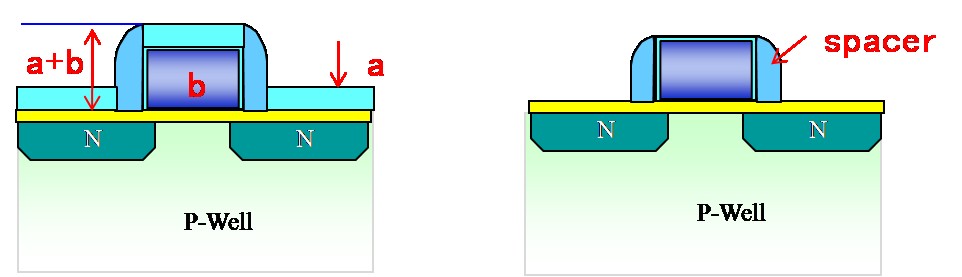

那这个Spacer是怎么形成的呢?看下面的示意图,假设Spacer的沉积的厚度是a,Poly的厚度是b,则在Poly边上的Spacer厚度是a+b。而我们的Spacer Etch是Blanket Etch (Etch back),而且记住这个Spacer Etch用的各向异性(Anisotropic)蚀刻,所以等效的理解为只有向下蚀刻,没有侧向蚀刻,所以如果我们吃掉的量为厚度a,则Poly边上会因为厚度太厚,剩下一块Spacer残留,这就是我们要的Spacer了。而它的Spacer宽度就是LDD的长度,而它的宽度是由Spacer的厚度决定的。(当然蚀刻自己也会影响,而宽度的关系自己理解吧~)